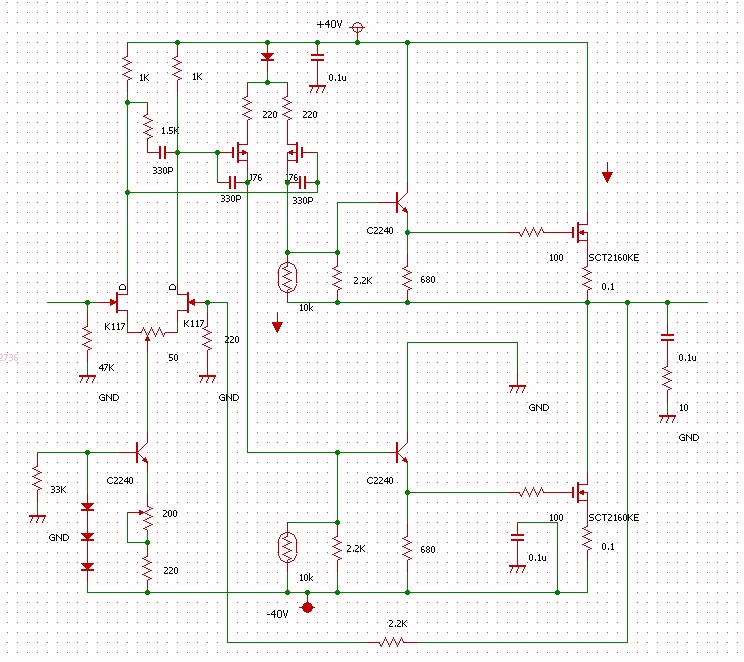

今回作ろうとしている回路

. 超広帯域電圧増幅段SiC MOSアンプ

ドライバー段にft 6GHzの2SC4703を用いる。Dualgate

MOSよりもさらに広帯域となる。±40の電源に対応する。

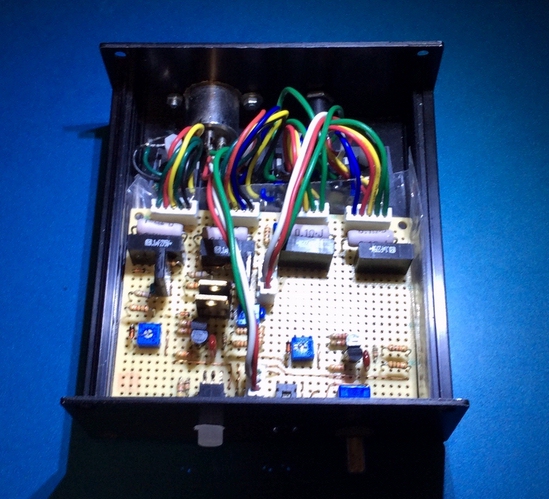

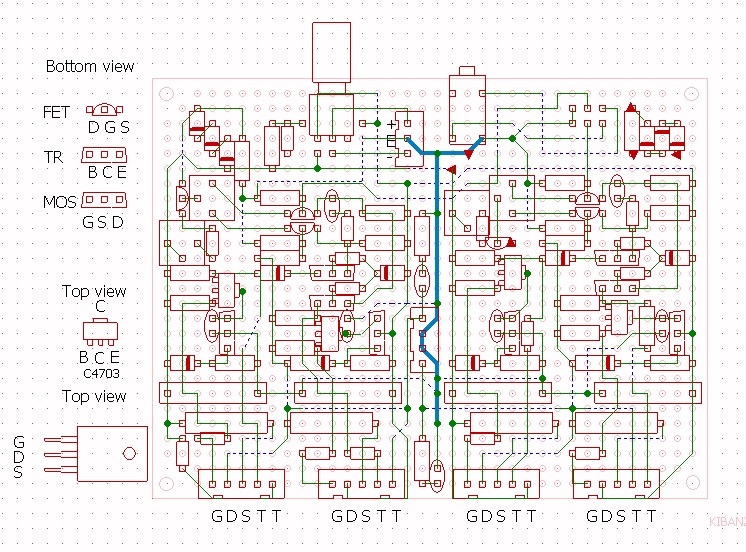

去年作ったA6のアンプ基板をリユースするので経済的である。

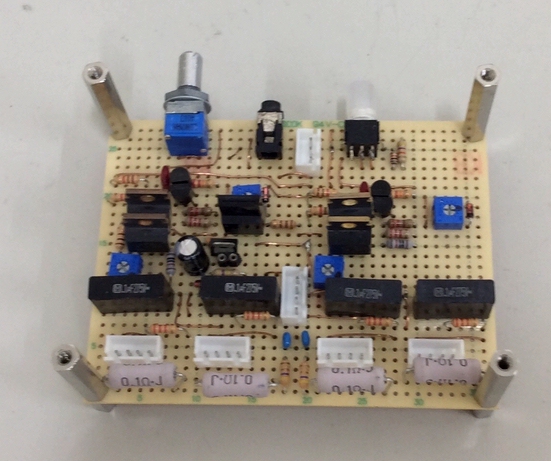

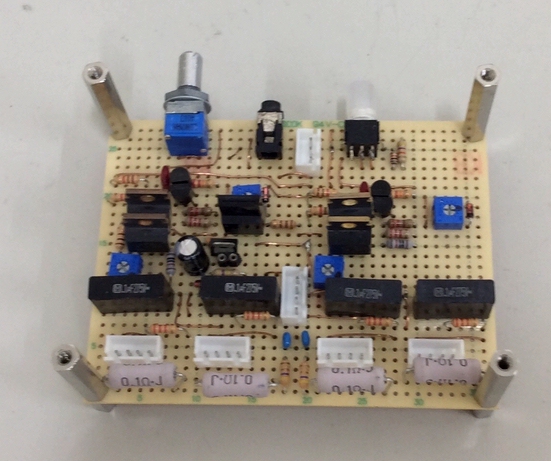

改造前の基板

今回作ろうとしている回路

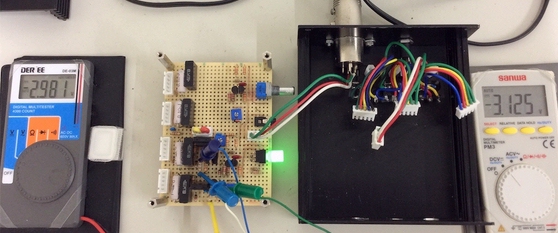

片chを組み終わって調整可能なところまで来た。

出力も充分取れているようだが測定してみると高調波歪みが多すぎることがわかった。大抵は出力の低いところでは

0.1%まで下がるのだが全然下がらない。負荷を5kΩにすると歪みは消滅するという現象がある。

位相補正を増やして(寄生発振は止まった)、二段目の電流も増やして(関係なかった)、アイドリングも増やして

(効果が薄い)、二段目のドレイン電圧のバランスを取るためにツェナーを入れるところまで試したところ、サーミスタ

が吹っ飛んでしまった。これは線材が入り込んだ事によるショート事故と推測している。補修からやり直しである。

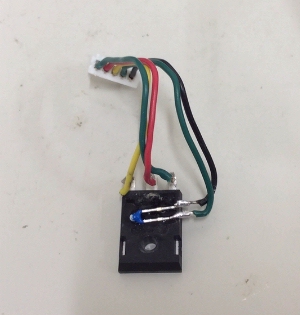

サーミスタの補修に取り掛かる。

瞬間接着剤とはいえ一晩寝かせてから半田付けした。

電圧増幅段のテスト

ドライバー段はC2240に変更している。三歩進んで二歩下がるである。最初から一歩進めば?と思うかもしれないが、

こちらの方が研究手法としてはいいのではないだろうか。

C2240をドライバーにしたアンプ

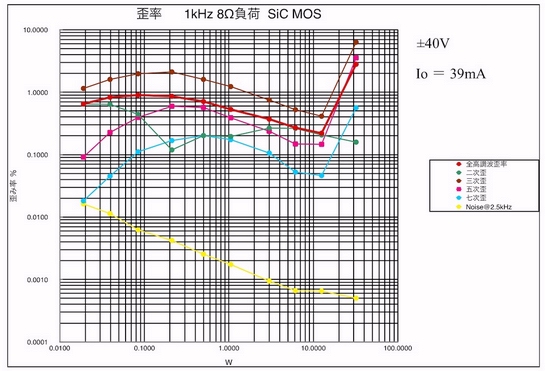

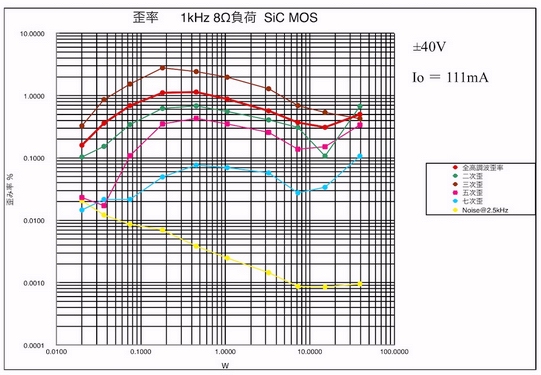

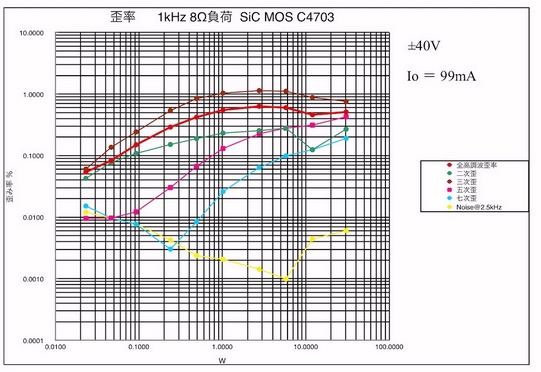

測定結果

出力は取れているようだが歪みが多い。金田式ではアイドリングに少なくとも150mAは流しているのでやってみる。

上手くいったようだが、早めにクリップするのが問題である。二段目の差動アンプがあやしいので対策を考える。

ほぼ金田式をコピーした回路。二段目がソース接地になっている。差動よりもダイナミックレンジが大きく取れる。

少なくとも二段目でのクリップは避けられる。

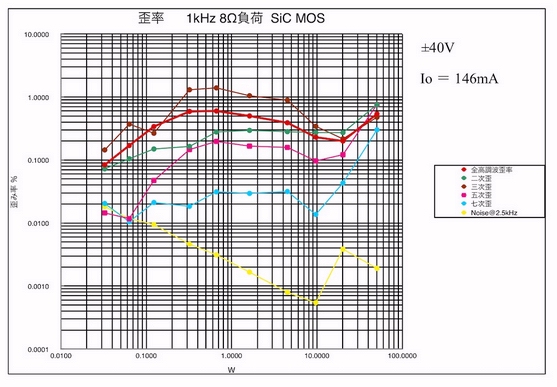

測定結果

まだクリップしているようだ。初段をK117GRからBL(IDSS=8.2mA)に変更する。

随分なだらかになっている。歪みが多いのは終段石の素性と思われるのでアイドリングを鬼のように流せば改善するだろう。

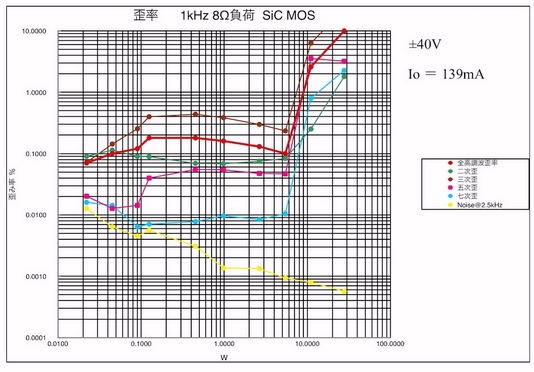

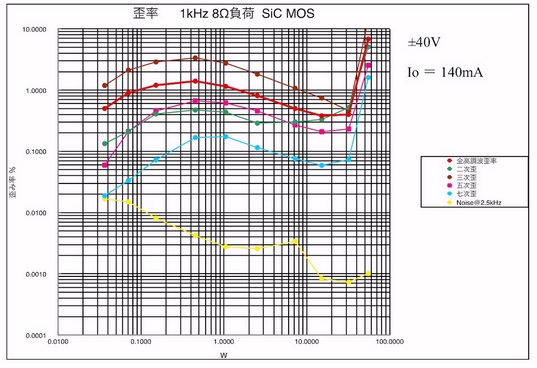

ファンで冷却しながら150mA流してみた。

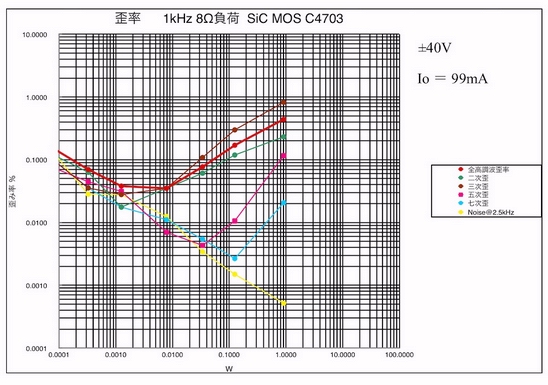

C2240ドライバー

50Wでもハードクリップしていない。小出力時に歪みが増加するのはアイドリング激増時にサーミスタが暖められて、

アイドリングが減少してしまうからだ。サイン波信号は大きい順に5秒づつ再生されるためである。逆の順にすると改善

されるだろう。

C2240に電圧制限をかけた場合

40Wからハードクリップが起こり、歪みも全体的に増加しているようだ。

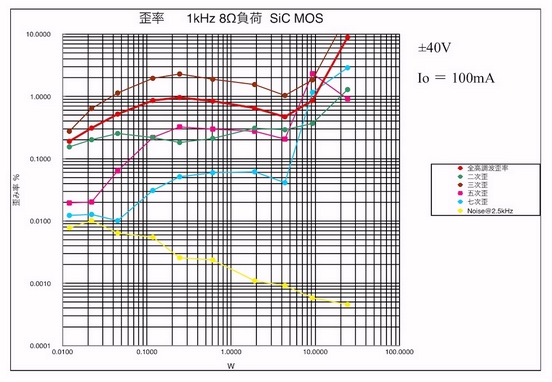

ドライバー段のC2240をC4073に変更した。40Wあたりでクリップするのがわかっているので低出力域で

測定した。

サーミスタの影響を受けないようにすれば歪みは直線的に下がってゆくのがわかる。

測定用の音声ファイルを編集して逆にしたものを用意したので使ってみた。小信号の方から測定する。

以前のものと比べると一目瞭然となっている。

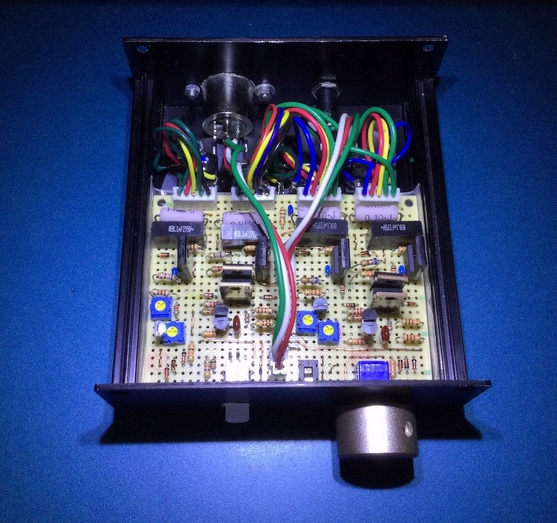

完成写真

試聴しながらアイドリングの安定度を見ている。

特に問題ないようだ。放熱器が小さいのでファンで温度を下げている。

やはりあらゆる点で最高点を叩き出すような鳴り方である。ダイナミックで透明、それでいてサラサラと

流れるように鳴る。ワイドレンジである。