これも長い間構想を練っていたがやっと形になってきた。A6のシャーシを用いる。

シミュレーターでは動作したが現物がどうなるかはまだ謎である。

SiC MOS-FETプリメインアンプ

これも長い間構想を練っていたがやっと形になってきた。A6のシャーシを用いる。

シミュレーターでは動作したが現物がどうなるかはまだ謎である。

回路図と基板図

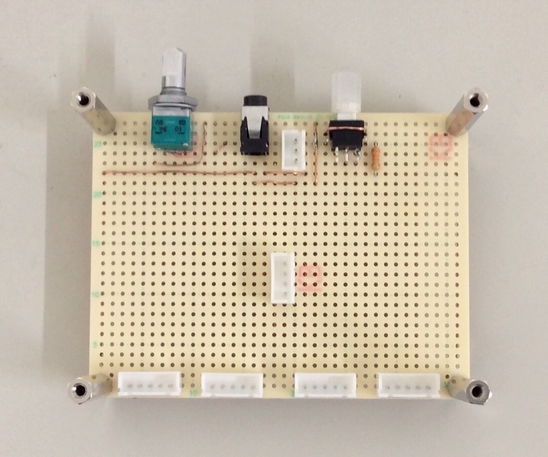

今回から5ピン端子を採用した。

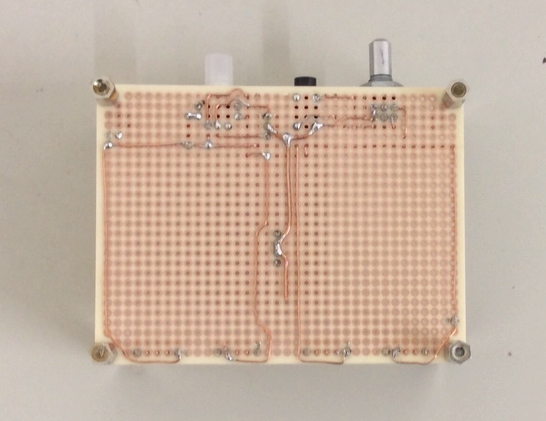

基板の電源周りまで作る。

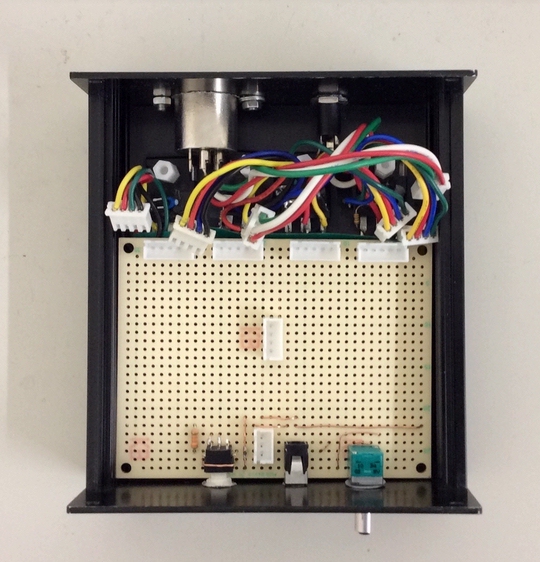

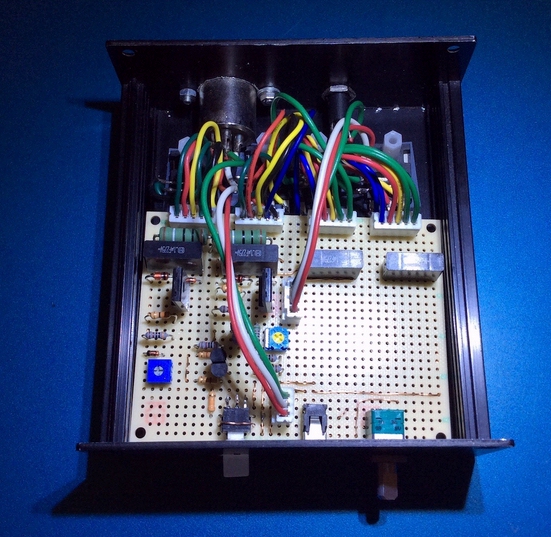

シャーシに収まるかどうか確認する。

LEDの点灯テスト

SiC MOS

のアンプは音がクッキリハッキリ出る割にはシンバルなどがハイ落ちに聴こえる。原因はドライバー段

にあるような気がしているのである。

Sic MOSはロームのものでも外国のものでもほとんど同じである。温度係数が正なので10kΩのサーミスタが貼り

付けてある。今回はサーミスタに端子に2ピン割り当てた。

電圧増幅段を調整しているところ。330Ωに終段のバイアス電圧を発生させている。

この後終段を接続して挙動を見たところ上手くいかなかった。バイアスを上げていっても終段のドレイン電流

が増加しなかった。おそらく発振である。

信号が通過するかどうかを見たが、高歪み、低出力のパターンだった。信号経路は正しく作られていると思う。

次にやる事は高周波トランジスタのC4703を取り外してチェックし、C1775Aあたりを試してみる事だ。三歩後退して

一歩進む感じである。

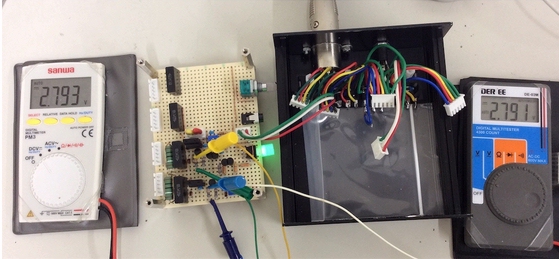

万事窮すだったが330pの位相補正を入れてみたら3.5Vのバイアス電圧が復活した。今は2.7Vになっている。

DCメカの状態で終段を入れたところ。8mA流れている。

NFBをかけてDCアンプにしたところ。アイドリング39mA、オフセット7.8mVになっている。

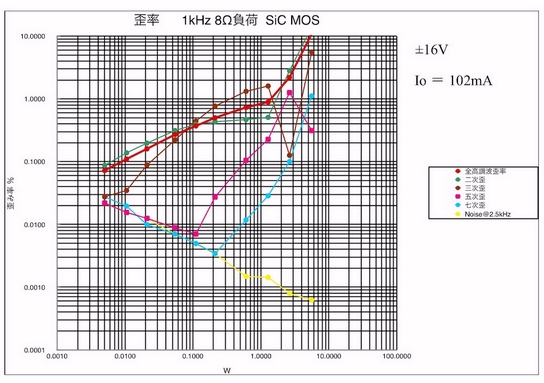

測定した。

低出力ながら正常動作しているのがわかる。

8Ω負荷出力が1Wも出ていないので改良を試みた。まずC1775AEを肩特性が良いC2240に替えてみた。

大して変わらなかった。次にJ103をIDSS=8mAのものに替える。すると調整不能の症状が出た。これは

IDSS=3.4mAのものに戻した。

やはりツェナーでドライバー段の電圧を制限しているのが悪そうなので取り払ってみた。勿論元に戻せる

ようにバイパスしただけである。

出力はよく出るようになったが歪みが多くなっている。ドライバー段の電流流し過ぎを疑って330Ω抵抗を

680Ωにしたが歪みはそれほど変わらなかった。

次に終段アイドリングを増やしたところ劇的に改善した。100mAにしたが200mAだともっと改善する。

びドライバー段の電圧制限(6.1V)を行うと前と同じように出力の低下が見られた。この問題の解決法は

電源電圧を高くするしかないような気がする。その実験はまた後で行うことにして、ドライバー段付きSiC

MOS アンプ

の完成を急ぐことにする。

決定した回路と定数

最近よく見るところの金田式だが温度補償の方法が異なっている。

組み上がったところ。

二段目の電流が要調整だったが上手くいったので試聴する。

気になっていたハイ落ちは解消し、全般的に聴きやすい音である。バランスがいい。低域の力感もあるし

高域のキラキラ感も少し残っている。バイポーラを入れることで音づくりができるようだ。

位相補正について調べてみる。

金田式位相補正なし

パターン1

パターン2

パターン3

パターン4

私の場合 位相補正なし

パターン1

パターン2

パターン3