±24Vの電源でSITアンプを製作する。各方式の最大出力を調べてみる。

これはLe Monstreを設計したHiraga氏の回路を参考にしたもの。9.2Wとなっている。

これはバイアス電圧を使った一般的な回路である。電圧の利用効率が悪い。6.9Wとなった。

これはネルソン・パス氏の回路を参考にしたもので効率が大変優れている。

少し改良して終段FETのVgsを直接ドライブするようにした。

SIT プッシュプルアンプ

±24Vの電源でSITアンプを製作する。各方式の最大出力を調べてみる。

これはLe Monstreを設計したHiraga氏の回路を参考にしたもの。9.2Wとなっている。

これはバイアス電圧を使った一般的な回路である。電圧の利用効率が悪い。6.9Wとなった。

これはネルソン・パス氏の回路を参考にしたもので効率が大変優れている。

少し改良して終段FETのVgsを直接ドライブするようにした。

回路図と基板図

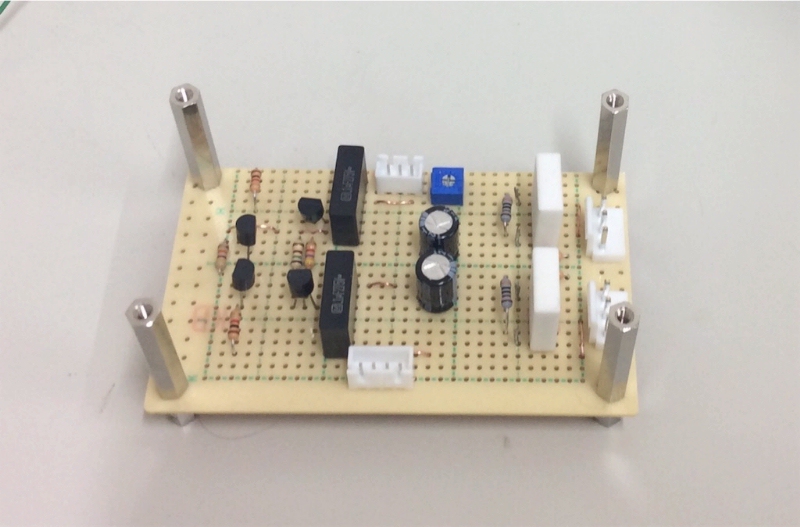

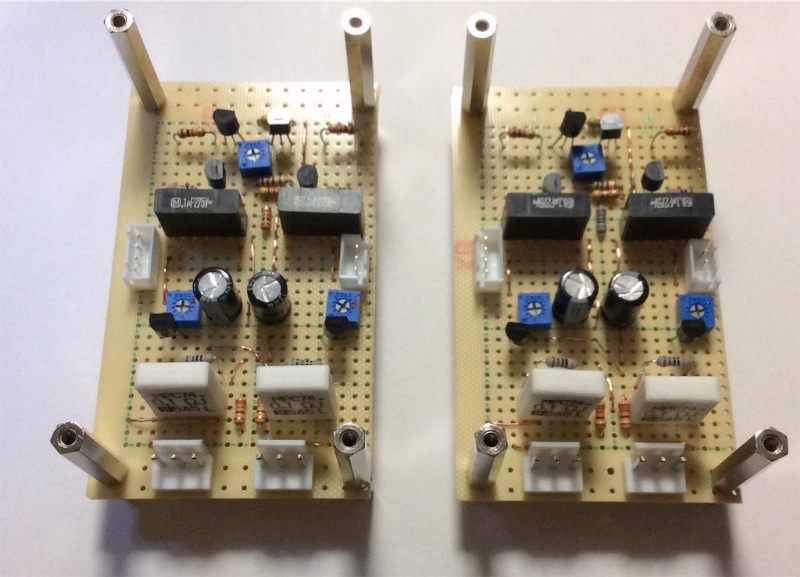

基板を作り始める。

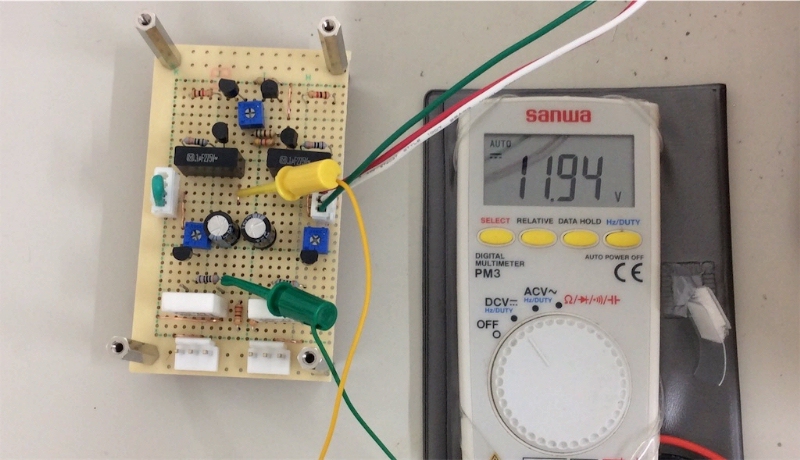

初段の電流がどうなっているか見る。これで2段目のエミッタ抵抗が決まる。330Ωに決定した。

バイアス生成はうまくいっている。ー12Vあれば大丈夫。

こちらもうまくいった。

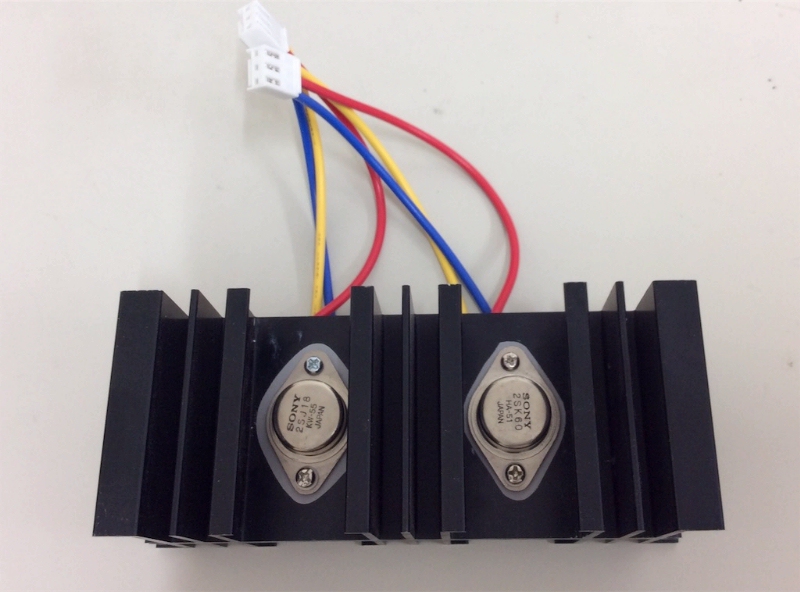

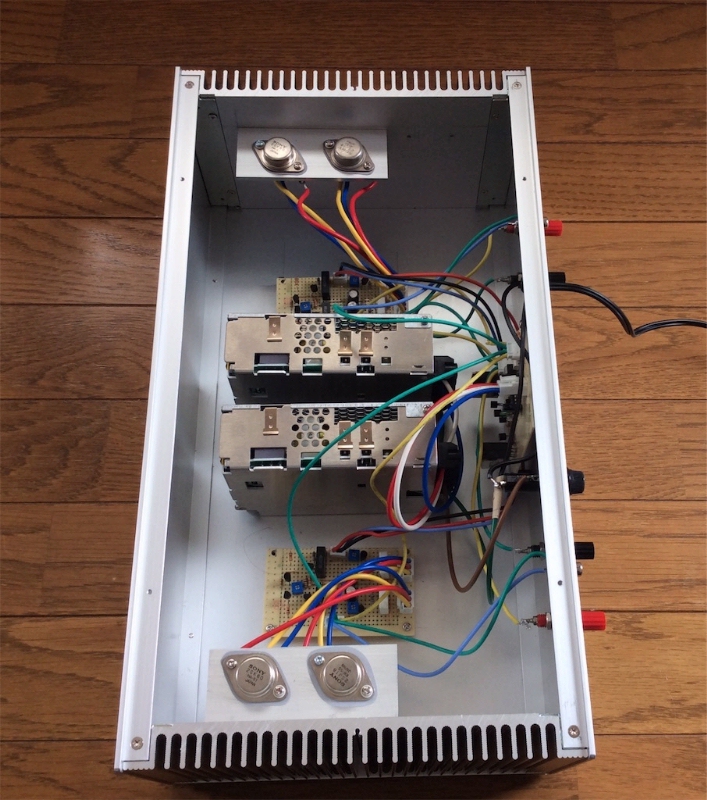

J18をつないでアイドリングを調整する。

K60の方も調整する。

これで終段が完成した。いわゆる直流電流メカの状態である。

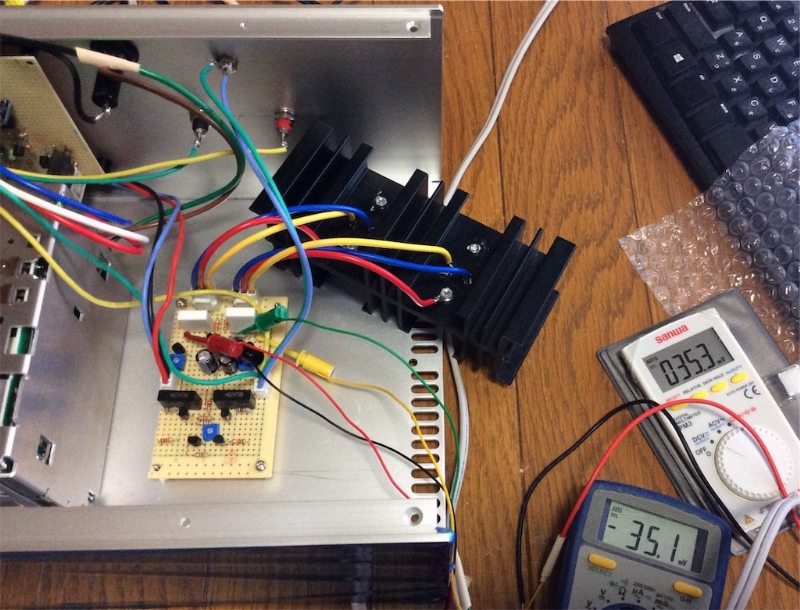

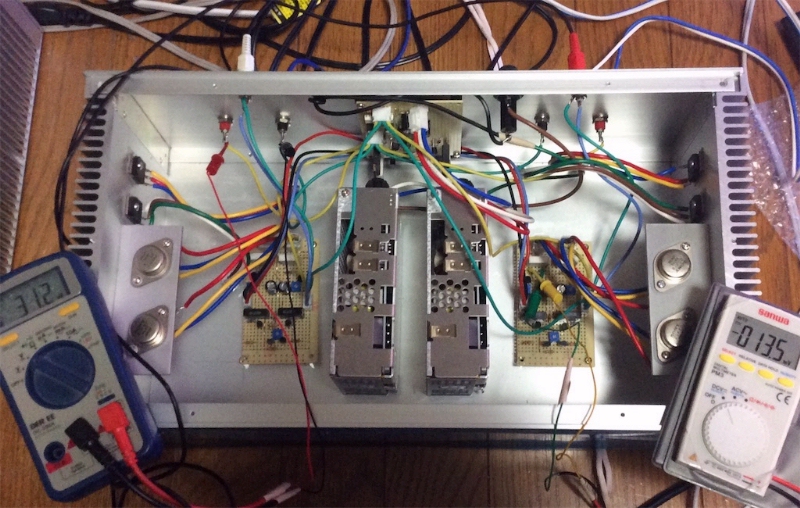

±24Vのアンプの電源でアイドリングを見る。350mAで安定している。

この時の特性を調べる。

できそうなので両ch作って完成を目指す。

安定動作するか安いスピーカーでテストする。アイドリング135mA、オフセット35mVとなっている。

ここまで来るのに紆余曲折があった。両ch起動だと保護回路が作動する。立ち上がりに6Aくらい流れるせいだと推測している。終段石が壊れることはなさそうなので保護回路をショートして運用している。Pass

VーFET POWERAMPのCSXー1

も保護回路無しなので大丈夫だろうと思う。音はとんでもないくらい良い。

この回路ではJーFETのランクにより初段の電流値が変わってくるのでその都度工夫する必要がある。本機では初段2.7?3.7mAになっている。K117はIdss=4mAのものを選別して終段バイアスの初期値をー12Vにすると安全である。調整時はこの状態から徐々にバイアスを浅くしてゆく。ただしこの回路では電源投入時にゼロバイアスになるようなので場合によっては成立しないこともあるだろう。

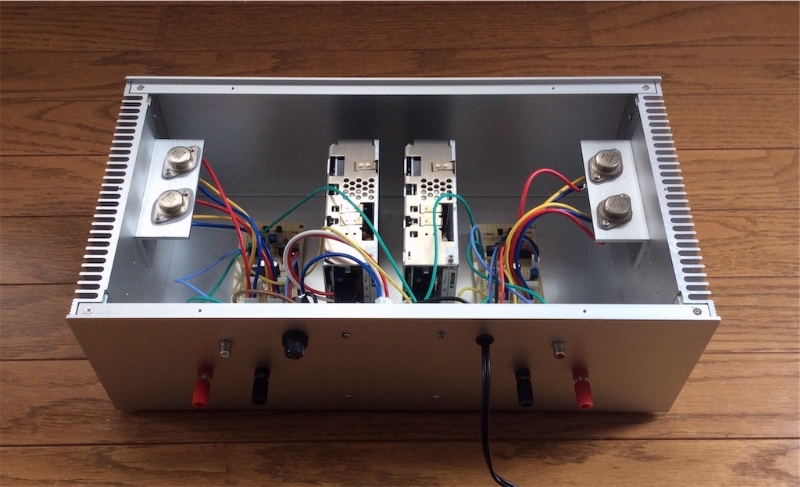

ひとまず完成したので全体像を示す。音は明るくふんわりとしたもので、K180が普通のSITとすると、SONYのVーFETは完熟の味がある。

保護回路を手直しして起動時の問題は回避できた。片ch毎に5.5Aまで作動しないようにした。

メインシステムで音を確認中。