D-NFBアンプの製作

これまでの検証を踏まえて一台作ってみることにする。

やはり直結回路を採用した。ドレイン出力なので出力Zoが十分低くないがD-NFBが改善してくれる。

Normal

D-NFB

Normal

D-NFB

超絶低歪になるというわけでもない。シミュレーターなのでこれが理論上の限界を示している。が実用に耐えうるアンプであると言って

よいであろう。

しかしDCスイープもカーブトレーサーも次数別歪率も私の伝統芸のようになってきた。あと動くブロックダイヤグラム、JTRIMを使った

重ね合わせグラフィックという手法もある。アンプを扱う上でここまでのことができるシミュレーターはあまりないと思う。

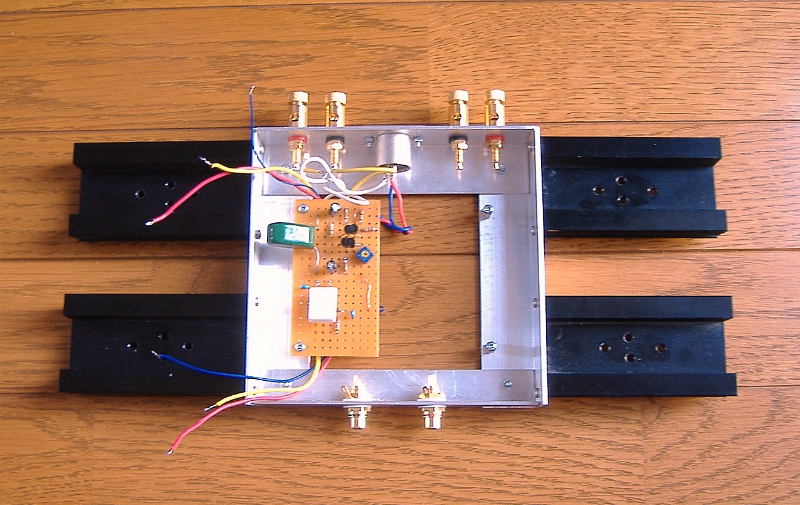

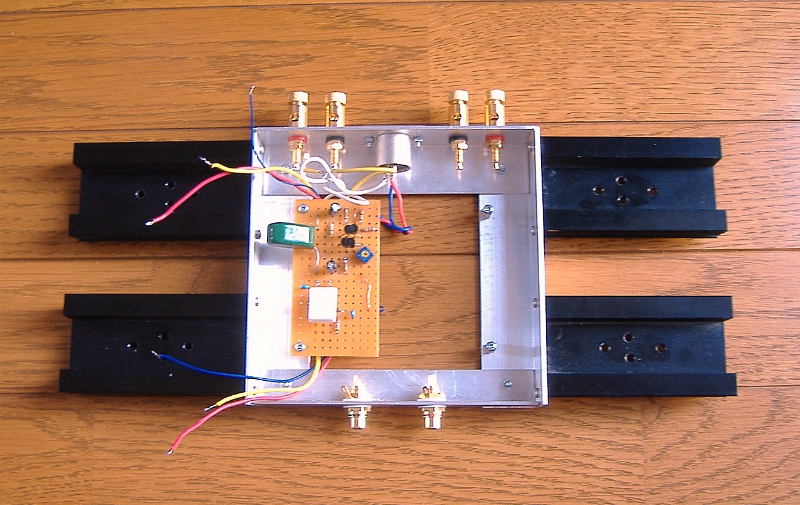

製作編

初段FETはIdss=7.9mAのペアを用意した。

この状態でゲートソース電圧を確かめておく。VR

Min→Center→ Maxで1.3→2.2→8Vとなる。このあとは一切基板を

はずさないで配線、調整が可能になった。

アイドリング 100mA

オフセット 200mV →43mV(D-NFB)

FETはあれほど高性能なのにコンプリにしたとたん半端でない二次歪を産生する。サンスイのMOSアンプがことごとくBTL

なのはそういう事情をあらわしているのだろう。完全対称では対称合成が効くが今度は三次歪が出てくる。フィードフォワードは

これらの特効薬となる。

さてD-NFBを見てみよう。シミュレーターに近い結果が得られている。簡単な仕掛けでフィードフォワードに匹敵する

改善を得る技術だと思う。

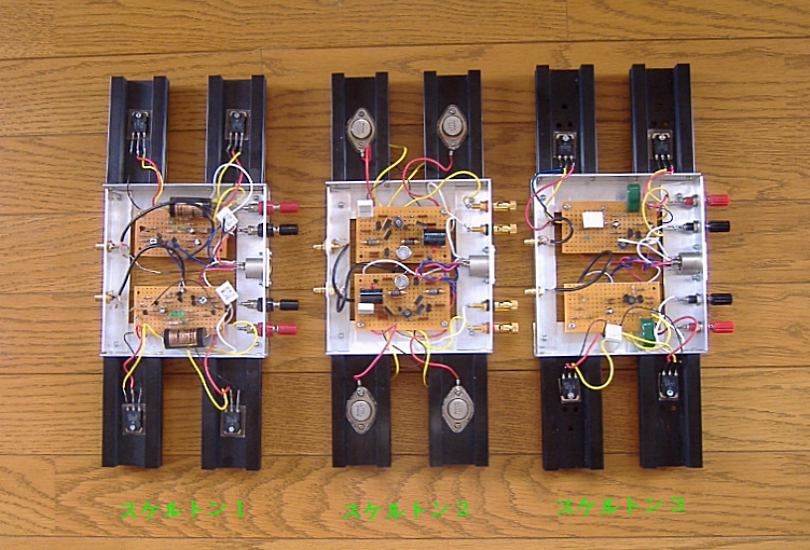

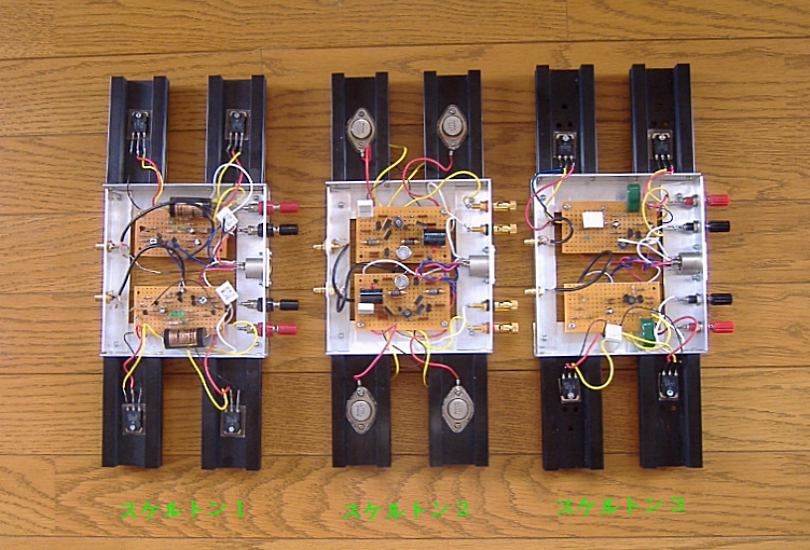

音もいいのでスケルトン3として完成させたい。

シリーズ完成。